The Future of Electronics: Building Up Instead of Out

The Limitations of Current Technology

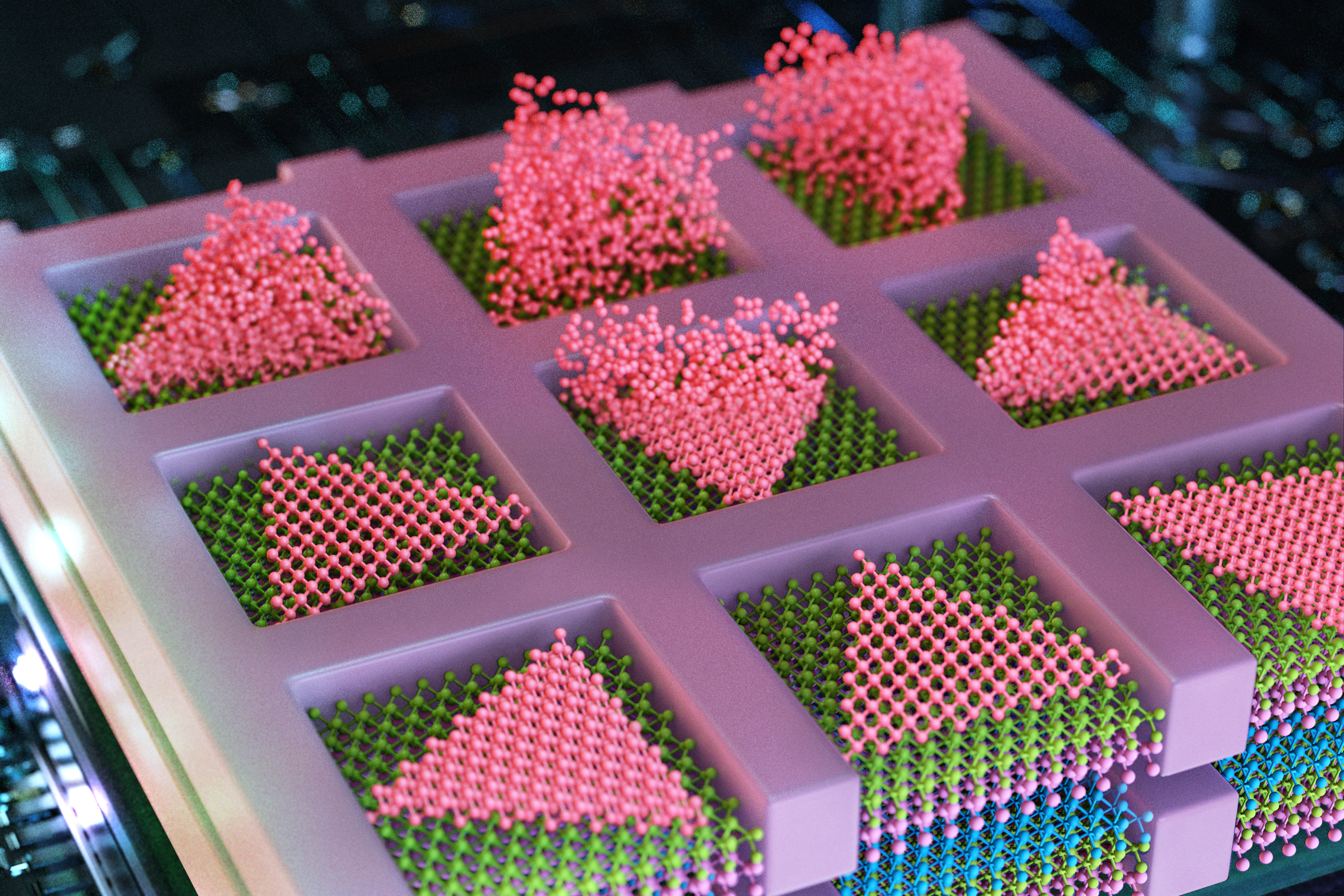

The electronics industry is approaching a limit to the number of transistors that can be packed onto the surface of a computer chip. To overcome this limitation, chip manufacturers are looking to build up rather than out. This means stacking multiple surfaces of transistors and semiconducting elements, similar to turning a ranch house into a high-rise. Such multilayered chips could handle exponentially more data and carry out many more complex functions than today’s electronics.

The Challenge of Stacking Chips

However, a significant hurdle is the platform on which chips are built. Today, bulky silicon wafers serve as the main scaffold on which high-quality, single-crystalline semiconducting elements are grown. Any stackable chip would have to include thick silicon "flooring" as part of each layer, slowing down any communication between functional semiconducting layers.

MIT Engineers’ Breakthrough

Now, MIT engineers have found a way around this hurdle, with a multilayered chip design that doesn’t require any silicon wafer substrates and works at temperatures low enough to preserve the underlying layer’s circuitry. In a study published in the journal Nature, the team reports using this new method to fabricate a multilayered chip with alternating layers of high-quality semiconducting material grown directly on top of each other.

How It Works

The method enables engineers to build high-performance transistors and memory and logic elements on any random crystalline surface – not just on the bulky crystal scaffold of silicon wafers. Without these thick silicon substrates, multiple semiconducting layers can be in more direct contact, leading to better and faster communication and computation between layers, the researchers say.

The Future of AI and Computing

The researchers envision that the method could be used to build AI hardware, in the form of stacked chips for laptops or wearable devices, that would be as fast and powerful as today’s supercomputers and could store huge amounts of data on par with physical data centers. "This breakthrough opens up enormous potential for the semiconductor industry, allowing chips to be stacked without traditional limitations," says study author Jeehwan Kim, associate professor of mechanical engineering at MIT. "This could lead to orders-of-magnitude improvements in computing power for applications in AI, logic, and memory."

Conclusion

The development of stackable chips has the potential to revolutionize the electronics industry, enabling the creation of faster, more powerful, and more efficient devices. With the help of this new technology, we can build AI hardware that is more powerful and efficient, leading to significant advancements in various fields, from healthcare to finance to education.

Frequently Asked Questions

Q: What is the purpose of the new method?

A: The new method enables the fabrication of multilayered chips without the need for silicon wafer substrates, allowing for faster and more efficient communication between layers.

Q: How does the new method work?

A: The method uses a technique known as "nucleation" to grow single-crystalline 2D materials at low temperatures, allowing for the creation of high-quality semiconducting materials on any random crystalline surface.

Q: What are the potential applications of this technology?

A: The technology has the potential to be used to build AI hardware, such as stacked chips for laptops or wearable devices, that would be as fast and powerful as today’s supercomputers and could store huge amounts of data on par with physical data centers.